Design of four variable function using MSI ICs

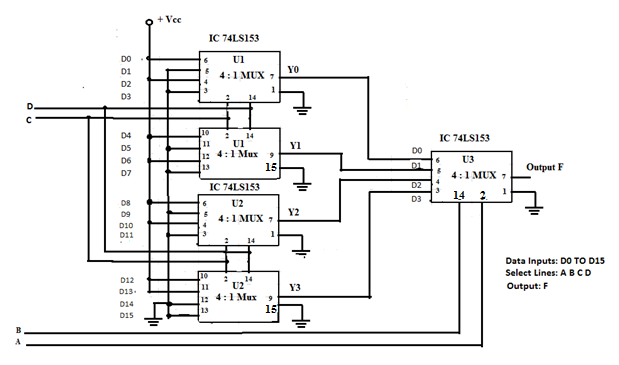

In Experiment # 1 we studied the use of IC 74LS153 as a Dual 4:1 MUX. We required only one IC 74LS153 to design an 8:1 MUX. Now in Experiment # 2 we shall study the application of MUX as a Universal Logic Generator for a four variable system.

To implement a four variable Universal Function Generator using IC 74LS153, let us follow these steps:

1. To begin with we shall design a 16:1 MUX using multiple 74LS153 ICs.

2. IC 74LS153 has two 4:1 MUXes within it. Each MUX has two select lines and four data input lines. So in all eight data inputs D0 to D7 are available from first IC # U1.

3. Similarly second IC # U2 provides another eight data inputs D8 to D15. Thus in all 16 input lines are now available.

4. To select one of these 16 data inputs, we need four select lines; let us label them as A B C & D; where A is the most significant bit (MSB) and D is the least significant bit (LSB).

5. Each IC has 4 select lines.

6. All eight select lines of U1 and U2 are connected together and labelled as select lines C & D.

7. To get additional two select lines we introduce the third IC U3. Only one 4:1 MUX of U3 is required. The two select lines of U3 are labelled as A & B.

8. The strobe inputs 1G’ & 2G’ of all the ICs is connected to ground so that all the IC’s are enabled for operation.

9. Thus in all we need three IC’s for the design of 4-variable Universal Logic Generator as shown in Fig.1.

The output function F can be written as:

F = A’.B’.Y0 + A’.B.Y1 +A.B’.Y2 +A.B.Y3

Fig.1. Four variable - Universal Logic Function Generator

The function table for Fig.1 is given below. Any four variable logic function can be derived using this circuit.

|

Decimal |

Select Lines |

Output |

|||

|

Equivalent |

A |

B |

C |

D |

Y |

|

0 |

0 |

0 |

0 |

0 |

D0 |

|

1 |

0 |

0 |

0 |

1 |

D1 |

|

2 |

0 |

0 |

1 |

0 |

D2 |

|

3 |

0 |

0 |

1 |

1 |

D3 |

|

4 |

0 |

1 |

0 |

0 |

D4 |

|

5 |

0 |

1 |

0 |

1 |

D5 |

|

6 |

0 |

1 |

1 |

0 |

D6 |

|

7 |

0 |

1 |

1 |

1 |

D7 |

|

8 |

1 |

0 |

0 |

0 |

D8 |

|

9 |

1 |

0 |

0 |

1 |

D9 |

|

10 |

1 |

0 |

1 |

0 |

D10 |

|

11 |

1 |

0 |

1 |

1 |

D11 |

|

12 |

1 |

1 |

0 |

0 |

D12 |

|

13 |

1 |

1 |

0 |

1 |

D13 |

|

14 |

1 |

1 |

1 |

0 |

D14 |

|

15 |

1 |

1 |

1 |

1 |

D15 |

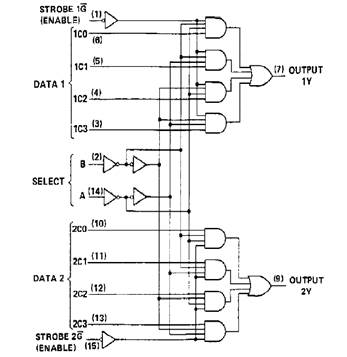

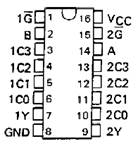

Fig. 2. Internal Structure & Pin Diagram of IC74LS153

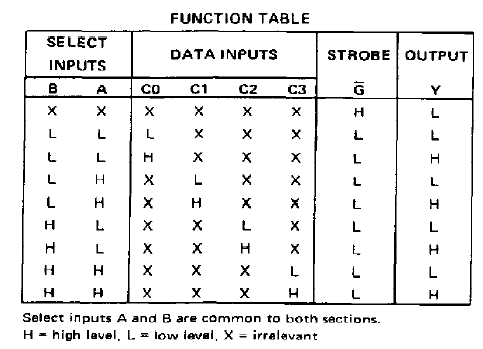

Fig. 3.Function Table

Numerical:

In 4-variable function, there are 4 select lines i.e. total 16 inputs (24 = 16).

| Select Lines | Inputs | Output | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| A | B | C | D | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | Y |

| 0 | 0 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 0 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 0 | 0 | 1 | X | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 0 | 0 | 1 | X | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 0 | 1 | 0 | X | X | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 0 | 1 | 0 | X | X | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 0 | 1 | 1 | X | X | X | 0 | X | X | X | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 0 | 1 | 1 | X | X | X | 1 | X | X | X | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 1 | 0 | 0 | X | X | X | X | 0 | X | X | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 1 | 0 | 0 | X | X | X | X | 1 | X | X | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 1 | 0 | 1 | X | X | X | X | X | 0 | X | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 1 | 0 | 1 | X | X | X | X | X | 1 | X | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 1 | 1 | 0 | X | X | X | X | X | X | 0 | X | X | X | X | X | X | X | X | X | 0 |

| 0 | 1 | 1 | 0 | X | X | X | X | X | X | 1 | X | X | X | X | X | X | X | X | X | 1 |

| 0 | 1 | 1 | 1 | X | X | X | X | X | X | X | 0 | X | X | X | X | X | X | X | X | 0 |

| 0 | 1 | 1 | 1 | X | X | X | X | X | X | X | 1 | X | X | X | X | X | X | X | X | 1 |

| 1 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | 0 | X | X | X | X | X | X | X | 0 |

| 1 | 0 | 0 | 0 | X | X | X | X | X | X | X | X | 1 | X | X | X | X | X | X | X | 1 |

| 1 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | 0 | X | X | X | X | X | X | 0 |

| 1 | 0 | 0 | 1 | X | X | X | X | X | X | X | X | X | 1 | X | X | X | X | X | X | 1 |

| 1 | 0 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | 0 | X | X | X | X | X | 0 |

| 1 | 0 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | 1 | X | X | X | X | X | 1 |

| 1 | 0 | 1 | 1 | X | X | X | X | X | X | X | X | X | X | X | 0 | X | X | X | X | 0 |

| 1 | 0 | 1 | 1 | X | X | X | X | X | X | X | X | X | X | X | 1 | X | X | X | X | 1 |

| 1 | 1 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | 0 | X | X | X | 0 |

| 1 | 1 | 0 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | 1 | X | X | X | 1 |

| 1 | 1 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 | X | X | 0 |

| 1 | 1 | 0 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | X | X | 1 |

| 1 | 1 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 | X | 0 |

| 1 | 1 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | X | 1 |

| 1 | 1 | 1 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 0 | 0 |

| 1 | 1 | 1 | 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 1 | 1 |

(Where : ‘1’ indicate VCC/+5V, ‘0’ indicate 0V, ‘X’ indicate “don’t care“)

Here we have implemented  :-

:-

D0, D2, D4, D6, D8, D10, D12, D13 to GND(Ground)

and D1, D3, D5, D7, D9, D11, D14, D15 to VCC(+5V)

So the resultant truth table is :

| Inputs | Output | |||

|---|---|---|---|---|

| A | B | C | D | Y |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |